Zuse

Добрый день. Проверили конфигурацию ядра RISC-V Ibex.

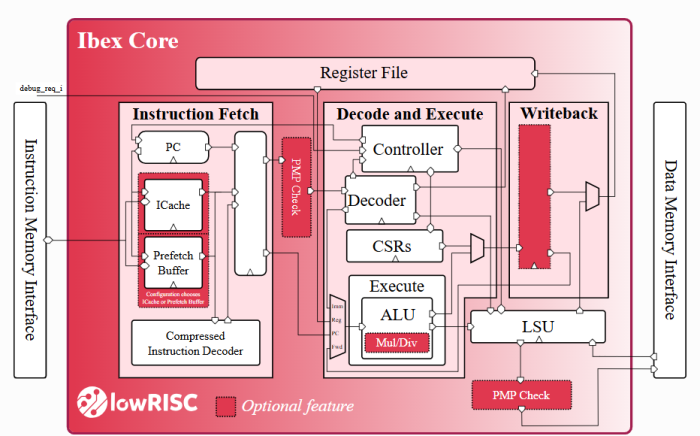

Стадии ядра, отмеченные красным цветом на изображении выше, являются опциональными и не используются в ИМС 5400ТР194. То есть в конвейере ядра есть только две стадии: выборка инструкции и исполнение инструкции.

Для блока умножения установлен параметр ibex_pkg::RV32MFast, то есть в соответствии с документацией на ядро операция MUL выполняется за 3 такта процессорного времени, операция MULH выполняется за 4.

Для блока работы с битовыми инструкциями установлен параметр ibex_pkg::RV32BNone, то есть данные инструкции в ядре отключены.

Область расширенных регистров отключена (RV32E = 0), то есть ядро содержит 16 32-битных регистров. Для них используется модель FlipFlop регистров (установлен параметр “ibex_pkg::RegFileFF).